# Microprocessor Power Analysis by Labeled Simulation

Cheng-Ta Hsieh, Kevin Chen and Massoud Pedram

University of Southern California

Dept. of EE-Systems

Los Angeles CA 90089

### **Outline**

- Introduction

- **Problem Formulation**

- Source and Sink

- Architecture Patterns

- Propagation Rules

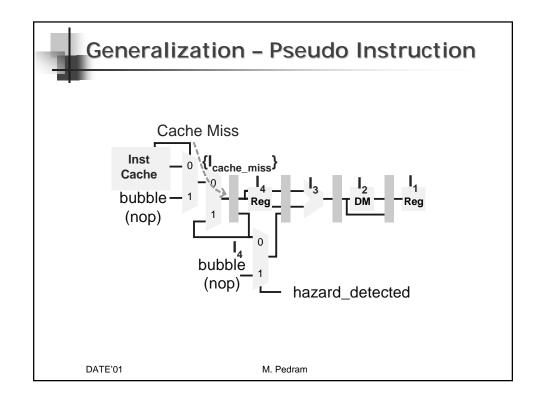

- Generalizations

- Conclusions

DATE'01

### Macro-Analysis vs. Micro-Analysis

- Macro-Analysis can answer the questions:

- How long the battery of a notebook computer can last if we run the Internet Explorer?

- Is MIPS more power-efficient than Strong ARM for running Windows CE 2.0?

- Micro-Analysis can answer the questions:

- What is the power consumption of a branch instruction, or a compare instruction?

- How much power is consumed in some component for a certain instruction?

DATE'01

M. Pedram

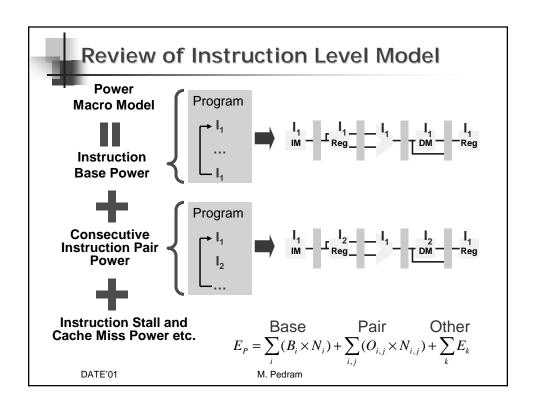

### Instruction Level Macro Modeling

- Instruction Base Costs

- Individual instruction

- Effect of Circuit State

- Consecutive instruction pair

- Inter-Instruction Effects

- Pipeline stall, cache misses

DATE'01

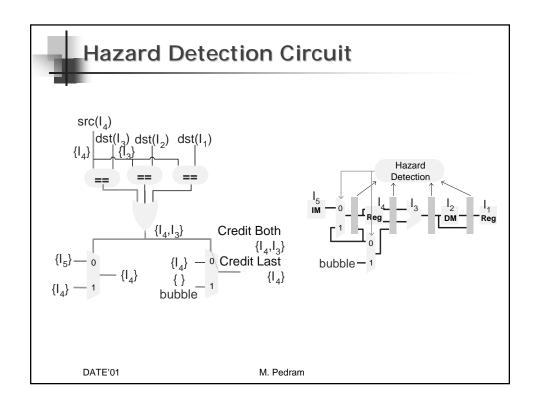

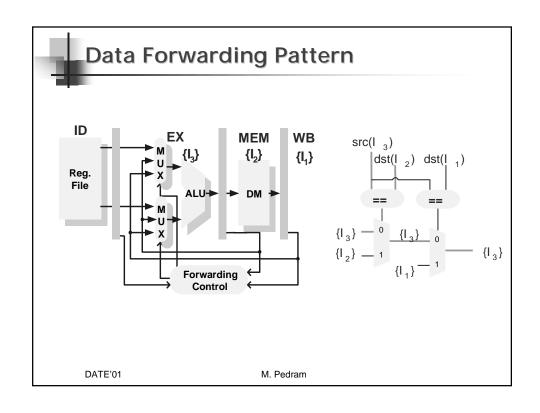

### **Problem Formulation**

- Given N gates,  $g_1, g_2, ..., g_n$  in a processor and k active instructions  $I_1, I_2, ..., I_k$

- For each gate  $g_i$ , find an instruction set or a labeling,  $L_j = \{I_1, ... I_m\}$ , such that the energy consumption of the gate in the current clock cycle is caused by instructions in  $L_i$

- Calculate instruction power consumption by label propagation

DATE'01

# Cycle-Accurate Energy Calculation

- Let *gates(I)* denote the set of label indices that contain instruction *I*

- Energy consumed by instruction *I* in the current clock cycle is:

$$E(I) = \frac{1}{2} \sum_{j \in gates(I)} \frac{1}{|L_j|} C_j V_{dd}^2 s w_j$$

DATE'01

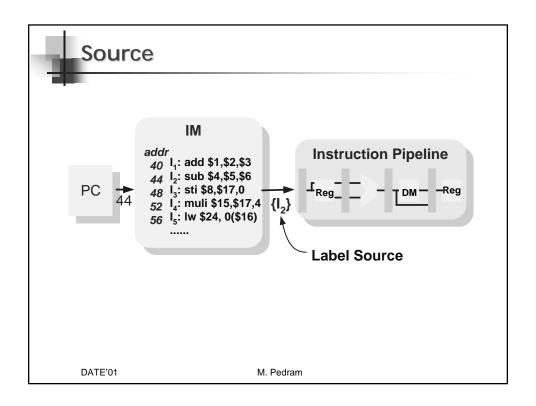

### **Definitions**

#### Source

Set of gates (or wires) from which the labels are originated

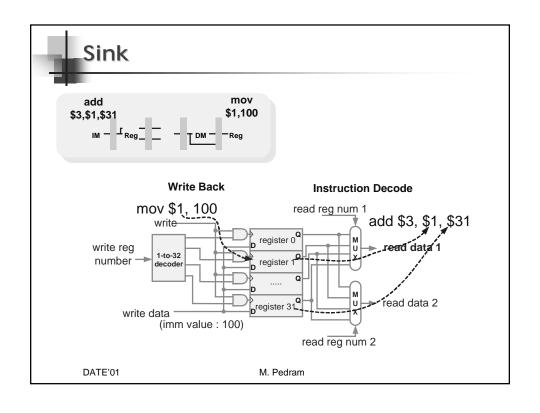

#### ■ Sink

Set of gates (or flip-flops) where the instruction label is dropped

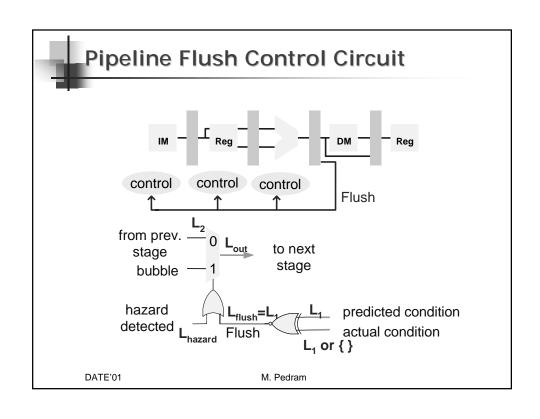

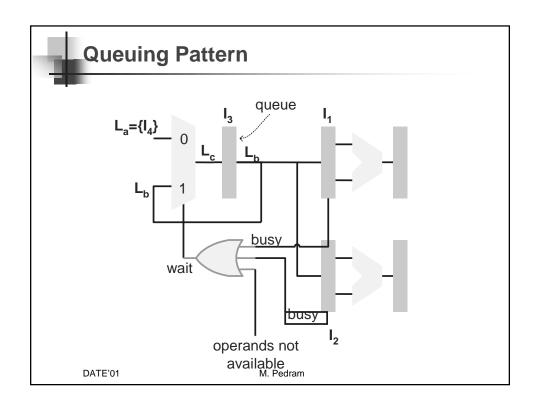

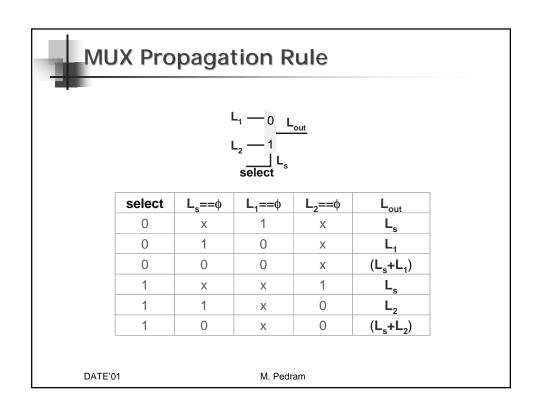

#### Label Propagation Rule

A description of how the labels are propagated through FSM's, MUX's, FF's, and primitive gates

DATE'01

M. Pedram

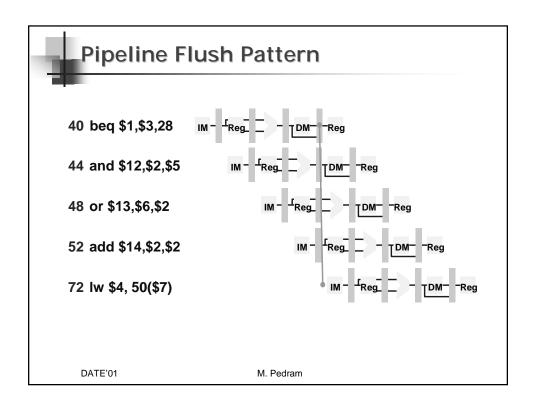

### **Architecture Pattern**

#### Name

The handle that is used to described the intended architecture effect (e.g., pipeline-flush, pipeline-stall, data-forwarding)

#### Description

Explanation of how the pattern is caused and how the processor reacts to the pattern

#### Liable Set

Set of instructions that are responsible for the power dissipation caused by the architecture pattern

#### Required Rule

Specification of how the propagation rule should work in response to the pattern

DATE'01

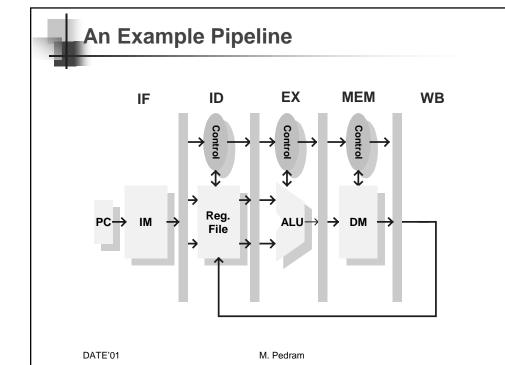

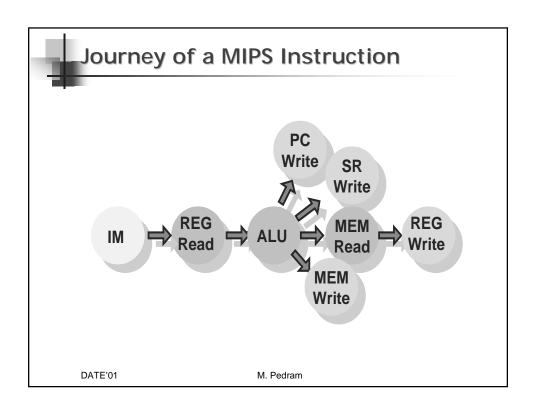

### An Architecture Pattern Example

- Name

- Streamlined Execution.

- Description

- Each pipeline stage performs the operation specified by the incoming instruction

- Liable Set

- The instruction being executed in a pipeline stage is responsible for the power dissipation of that stage

- Required Rule

- The instruction label in a pipeline is transferred to the next stage in the next clock cycle

DATE'01 M. Pedram

### Feasible Labeling Problem

- Given a

- set of architecture patterns.

- Find the

- set of sources

- set of sinks

- set of label propagation rules

- that satisfy all the required rules in the set of architecture patterns

DATE'01

### Implication by Domination

- An architecture pattern is dominated by a combination of other patterns if its required rules are covered by the required rules of these architecture patterns

- A labeling scheme is feasible for a target processor if all of the architecture patterns of that processor are dominated by the architecture patterns that are captured by the labeling scheme

DATE'01

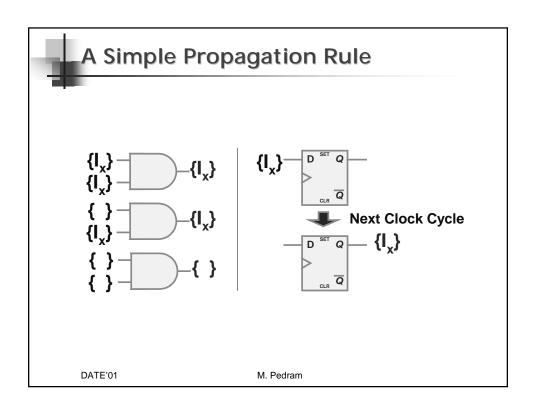

## **General Propagation Rules**

### Primitive Gates

### ❖ OR Gate

| L <sub>out</sub>               | in <sub>2</sub> | in₁ |

|--------------------------------|-----------------|-----|

| L <sub>1</sub> +L <sub>2</sub> | 0               | 0   |

| L <sub>1</sub>                 | 0               | 1   |

| L <sub>2</sub>                 | 1               | 0   |

| L <sub>1</sub> +L <sub>2</sub> | 1               | 1   |

Priority Rule:

If

$$L_1 = \{I_j\}$$

,  $L_2 = \{I_j\}$ ,

then  $L_1 + L_2 = \{I_{max(i,j)}\}$

Union Rule:

$$L_1+L_2=L_1\cup L_2$$

DATE'01

M. Pedram

### Rules for Primitive Gates (cont'd)

#### ❖ AND Gate

| in <sub>1</sub> | in <sub>2</sub> | L <sub>out</sub>               |

|-----------------|-----------------|--------------------------------|

| 0               | 0               | L <sub>1</sub> +L <sub>2</sub> |

| 1               | 0               | L <sub>2</sub>                 |

| 0               | 1               | L <sub>1</sub>                 |

| 1               | 1               | L <sub>1</sub> +L <sub>2</sub> |

### ❖ XOR Gate

| in <sub>1</sub> | in <sub>2</sub> | L <sub>out</sub>               |

|-----------------|-----------------|--------------------------------|

| 0               | 0               | L <sub>1</sub> +L <sub>2</sub> |

| 1               | 0               | L <sub>1</sub> +L <sub>2</sub> |

| 0               | 1               | L <sub>1</sub> +L <sub>2</sub> |

| 1               | 1               | L <sub>1</sub> +L <sub>2</sub> |

DATE'01

#### An ARM arithmetic instruction

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

#### Operation

if ConditionPassed (<cond>) then

Rd = Rn <op> <shifter\_operand>

if S == 1 and Rd == R15 then

CPSR = SPSR

else if S == 1 then

N Flag = Rd[31]

Z Flag = if Rd == 0 then 1 else 0

C Flag = CarryFrom (Rn + <shifter\_operand>)

V Flag = OverflowFrom (Rn + <shifter\_operand>)

DATE'01 M. Pedram

# **Energy Calculation**

$$P = \sum_{n=1}^{x} (E_{in} \bullet sw_{in} \bullet 10^{-6}) + \sum_{n=1}^{y} (C_{on} \bullet Vdd^{2} \bullet \frac{1}{2} sw_{on} \bullet 10^{-6})$$

Cell Power

Net Power

$P = power dissipation for current clock cycle (<math>\mu J$ );

x = number of input pins;

$E_{in}$  = energy associated with the n<sup>th</sup> input pin ( $\mu$ W/MHz)

y = number of output pins;

C<sub>on</sub> = external capacitive loading

DATE'01

M. Pedram

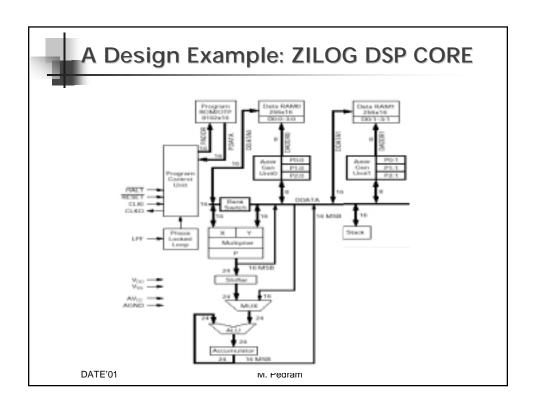

# **Experimental Results**

| <b>Instruction Class</b> | Average Energy(10 <sup>-8</sup> J) | Instruction<br>Count |

|--------------------------|------------------------------------|----------------------|

| NON                      | 0.0053                             | -                    |

| SL                       | 0.0262                             | 83                   |

| MAC                      | 0.0513                             | 132                  |

| CTRL                     | 0.0101                             | 30                   |

| CAS                      | 0.0147                             | 7                    |

| ALF                      | 0.0198                             | 14                   |

|                          |                                    |                      |

DATE'01

### Summary

- Proposed technique reports cycle-accurate (finegrain) power consumption for each instruction being executed in a pipelined (superscalar) machine

- Proposed technique helps identify power problems during the processor design phase

- Proposed technique is verified against MIPS, ARM, Pentium microprocessor, and a Zilog DSP

- Pseudo instruction and instruction splitting are useful for building a high-level macro-model that accounts for hard-to-capture power effects

DATE'01 M. Pedram