## Analysis of Non-Uniform Temperature-Dependent Interconnect Performance in High Performance ICs

Amir H. Ajami and Massoud Pedram University of Southern California

> Kaustav Banerjee Stanford University

Lukas P.P.P. van Ginneken *Magma Design Automation Inc.*

DAC'01

June 21st, 2001

#### **Presentation Outline**

- + Introduction

- **♦** Analysis of Non-Uniform Chip Temperature

- ★ Temperature-Dependent Interconnect Performance

- **←** Implications for Clock Skew

- ◆ Summary

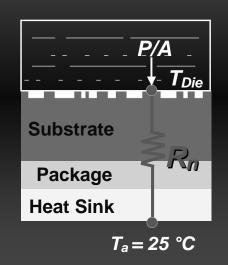

# **Average Chip Thermal Model**

◆ 1-D heat conduction model

$$T_{Die} = T_a + R_n \left( \frac{P}{A} \right)$$

♠ Due to excessive Joule heating and the distance from the heat-sink, global interconnect lines are the hottest locations inside the chip

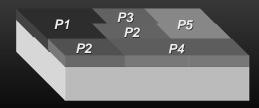

# **Non-Uniform Substrate Power Map**

- Substrate power generation distribution is generally non-uniform

- Functional block clock gating

- System-level power management

- Non-uniform distribution of gate sizing and switching activities in different blocks

# **Non-Uniform Substrate Temperature**

- Substrate thermal profile is non-uniform

- \* Thermal time constant is of the order of ms

- Switching activities in the block level are more important

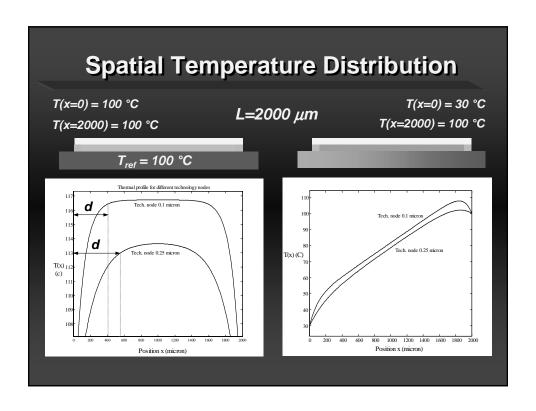

- Introduces non-uniformity in the global interconnect thermal profile

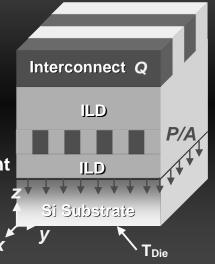

#### **Interconnect Thermal Profile**

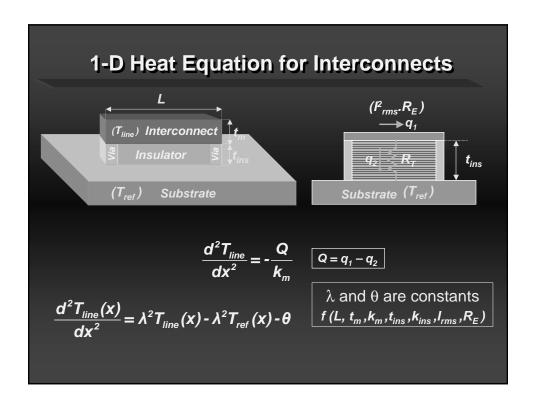

◆Three dimensional heat conduction in steady state

$$\nabla^2 T = 0$$

◆With an effective heat generation Q in the interconnect and a constant thermal conductivity k<sub>m</sub>

$$\nabla^2 T + \frac{Q}{k} = 0$$

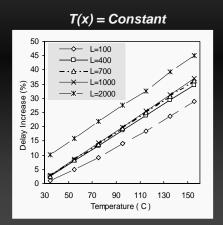

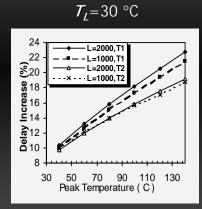

### **Temperature Dependency of Delay**

Interconnect delay dependent on T due to the T dependence of the resistance

$$r(x) = \rho_o(1 + \beta T(x))$$

- • $\rho_0$ : resistance per unit length at reference temperature

- •β: temperature coefficient of resistance (1/°C)

### **Non-Uniform Temperature-Dependent Delay**

◆ Distributed RC delay model

$$D = R_{d}(C_{L} + \int_{0}^{L} C_{o}(x)dx) + \int_{0}^{L} r_{o}(x)(\int_{x}^{L} C_{o}(\eta)d\eta + C_{L})dx$$

$$D = D_o + (c_o L + C_L) \rho_o \beta \int_0^L T(x) dx - c_o \rho_o \beta \int_0^L x T(x) dx$$

$D_0$  is the Elmore delay model at reference temp.

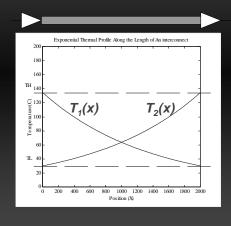

#### **Effects of Non-uniform Thermal Profiles**

Assume two exponential thermal profiles:

### **Direction of Thermal Profiles**

- ◆ Decreasing (increasing) thermal profile is equivalent to increasing (decreasing) sizing profile for uniform resistance wire

- Increasing thermal profile has better performance than that of decreasing thermal profile (optimal wire sizing)

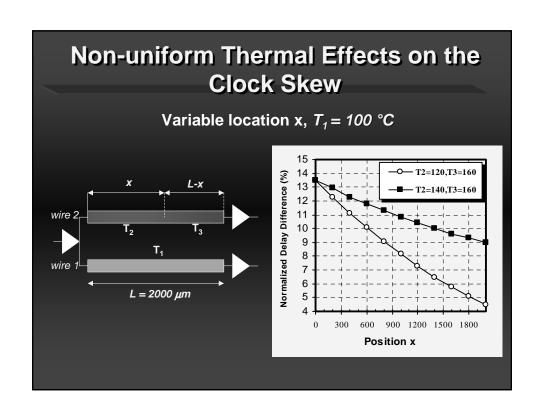

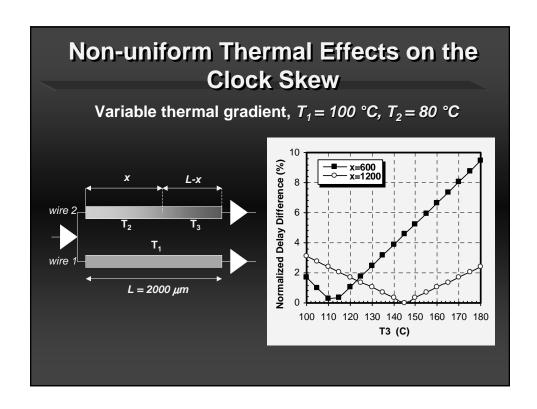

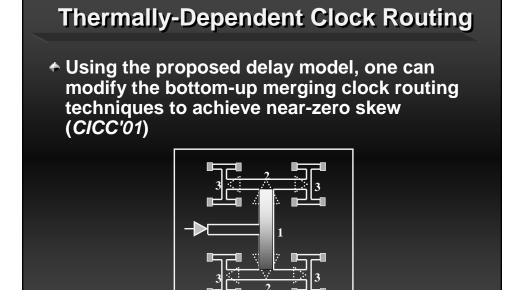

### **Clock Net Routing**

- Clock is the most vulnerable signal to the underlying thermal non-uniformities

- \* Usually driven by the highest current

- Have long global segments in the highest metal layers

- Clock nets must have near-zero skew among their sinks to guarantee correct functionality of the circuits

- ◆ Designing with a worst-case uniformtemperature is not sufficient from the clock net point of view

### **Summary**

- Due to different switching activities along with low power design policies, substrate & interconnect thermal maps are non-uniform

- **♦** Interconnect thermal non-uniformities:

- ♦ have significant impact on signal performances

- ◆ can introduce significant skew in clock trees

- may have serious impacts on different EDA flow steps: Buffer-insertion, Buffer-sizing, Gate-sizing, etc.

- Non-uniform interconnect thermal profiles must be considered in the design flow of highperformance VLSI systems