Pedram

High-Level Design Challenges and Solutions for Low Power Systems

Massoud Pedram

University of Southern California

Department of EE-Systems

Los Angeles CA 90089-256

Email: massoud@zugros.usc.edu

Outline

Introduction

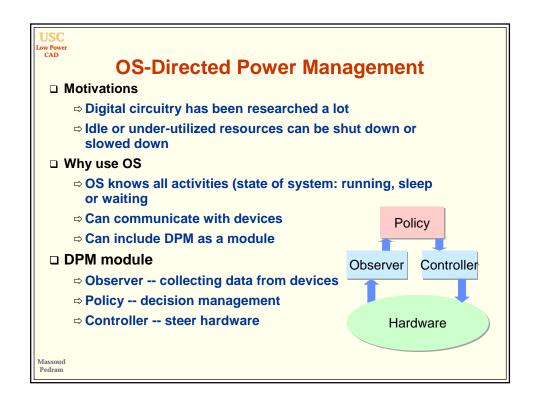

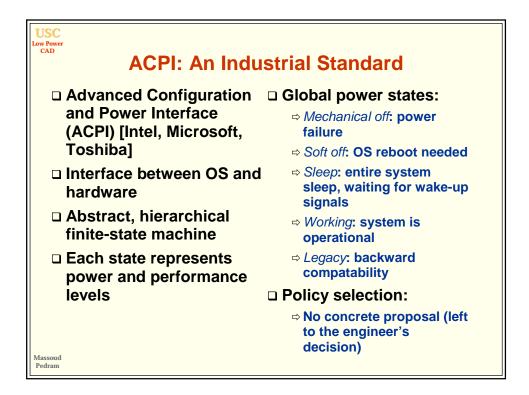

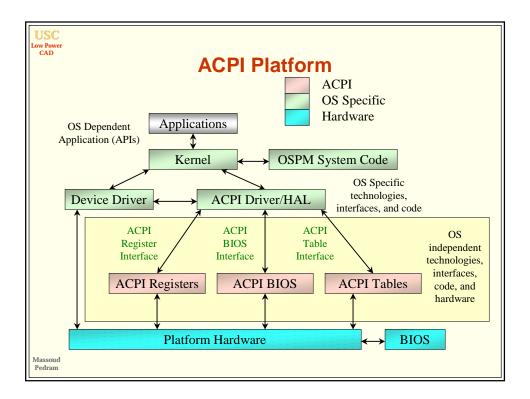

OS-Directed Power Management

Compiler-Based Power Optimization

Summary

USC Low Power

## **Process Technology Trend**

|                                                   | 1997   | 1999    | 2001    | 2003    | 2006    | 2009    | 2012    |

|---------------------------------------------------|--------|---------|---------|---------|---------|---------|---------|

| Min. Feature Size (µm)                            | 0.25   | 0.18    | 0.15    | 0.13    | 0.1     | 0.07    | 0.05    |

| Threshold Voltage (V)                             | 0.5    | 0.45    | 0.4     | 0.35    | 0.3     | 0.25    | 0.2     |

| T <sub>ox</sub> (nm)                              | 5      | 4       | 3       | 3       | 2       | 1.5     | 1       |

| C <sub>interconnect</sub> (aF/µm)                 | 50     | 36      | 29      | 21      | 20      | 16      | 14      |

| Memory @ samples/introduction (G)                 | 0.256  | 1       | *       | 4       | 16      | 64      | 256     |

| Max $I_{off}(\mu A/\mu m)$ (For minimum L device) | 1      | 1       | 3       | 3       | 3       | 10      | 10      |

| Minimum Supply Voltage (V)                        | 2.5    | 1.8     | 1.5     | 1.5     | 1.2     | 0.9     | 0.6     |

| On-chip across-chip clock freq. (MHz)             | 400    | 600     | 700     | 800     | 1100    | 1400    | 1800    |

| Off-chip peripheral bus freq. (MHz)               | 75/175 | 100/263 | 100/362 | 125/464 | 125/554 | 150/734 | 150/913 |

| ASIC usable xtors (millions / cm <sup>2</sup> )   | 8      | 14      | 16      | 24      | 40      | 64      | 100     |

| Chip size (cm <sup>2</sup> )                      | 3      | 3.4     | 3.85    | 4.3     | 5.2     | 6.2     | 7.5     |

| Chip-to-package (pad) count                       | 800    | 975     | 1195    | 1460    | 1970    | 2655    | 3585    |

Cost-Perf. Designs - notebooks, desktop personal computers, telecom

Massoud Pedram

Data extracted from NTRS'97

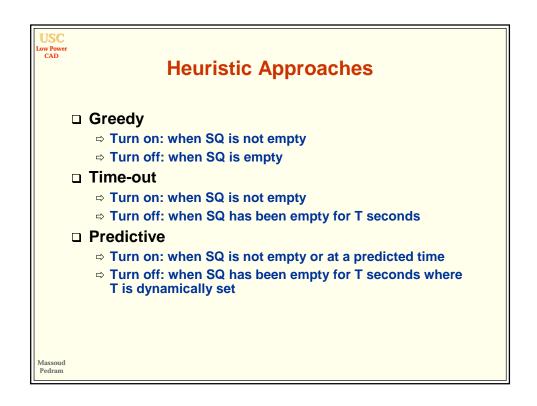

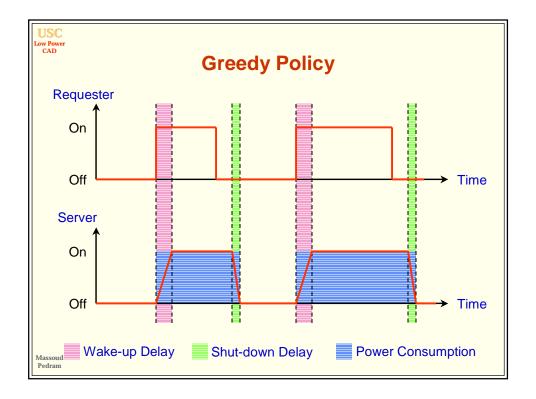

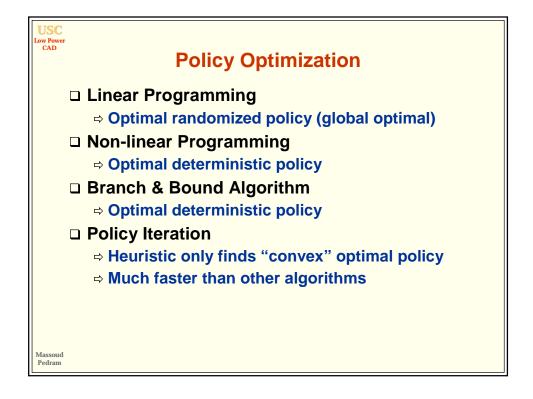

Shortcomings of Previous Approaches

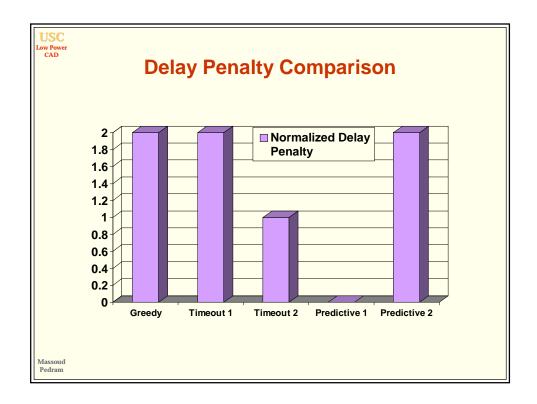

Performance highly depends on workload characteristics

No guarantee of optimality

Cannot handle more than two power states

Cannot handle complex systems

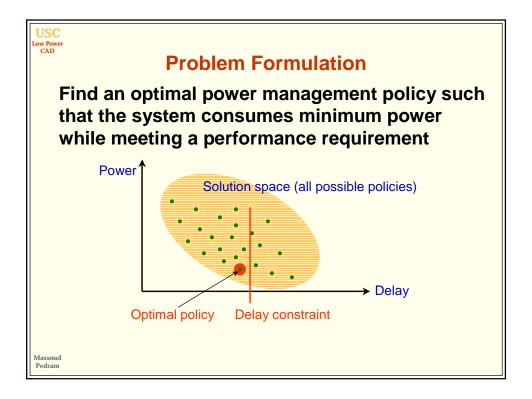

Stochastic Approaches

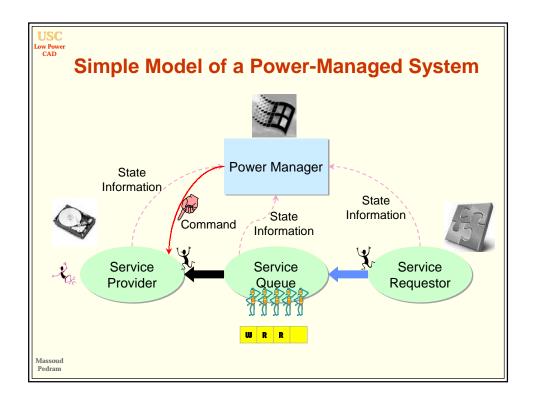

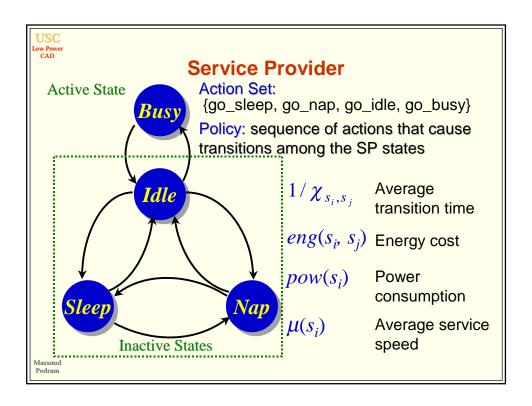

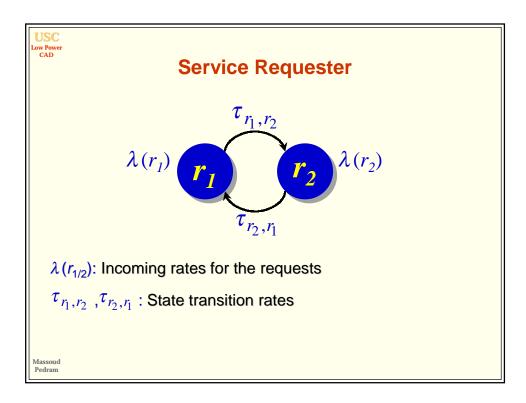

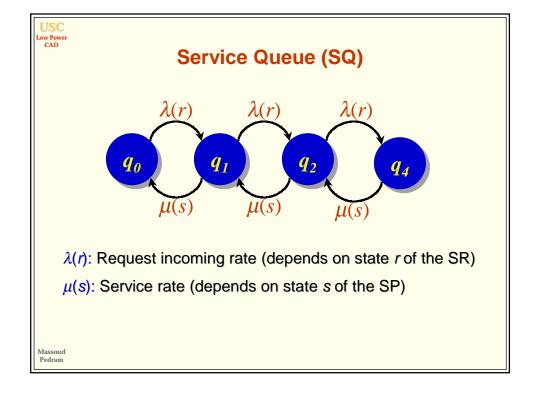

A generalized approach based on continuous-time Markov decision processes

Adaptive and efficient

Achieves optimal power under any given delay constraint (or vice versa)

Can be extended to handle non-stationary data, multiple servers and requesters, correlations among system state transitions

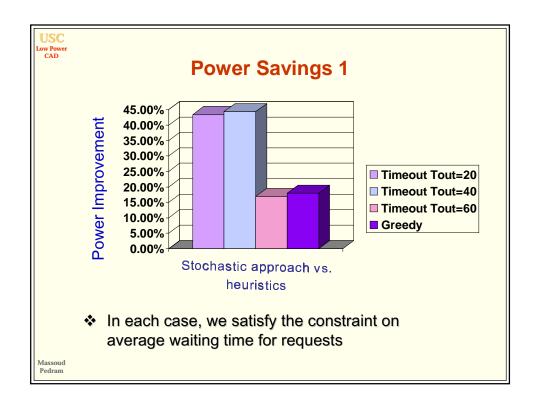

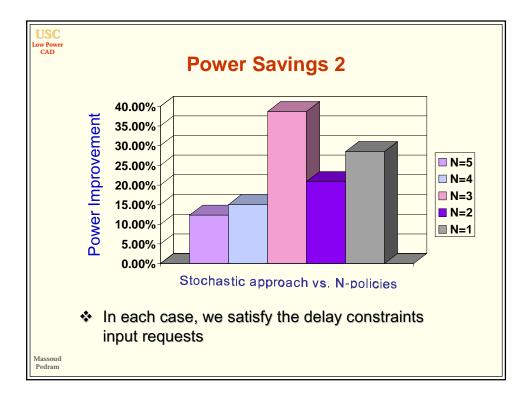

Experimental Setup

☐ Model construction

☐ SP model with four states

☐ SR model with one state

☐ SQ model of length 5

☐ Exponential distribution of request interarrival times

☐ Comparison with other approaches

☐ N-policy: Turn off the SP when the SQ is empty; Turn on the SP when there are N requests in the queue

☐ Optimal when SP has two states

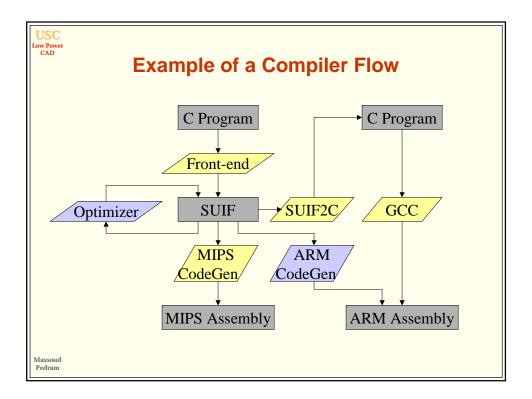

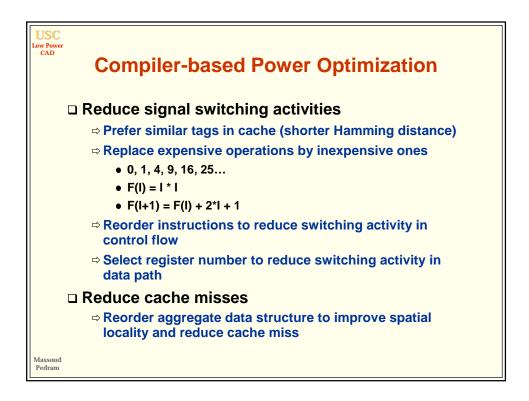

Power-Aware C/C++ Compilers

There exists a large amount of C/C++ code; rewriting them for low power is impractical. Instead we can recompile them for low power

A power-aware compiler can help in choosing the best hardware architecture

Compiler can insert commands into the application programs so that they can in turn provide detailed information to the OS for more effective power management

USC Low Power

## **Conclusions**

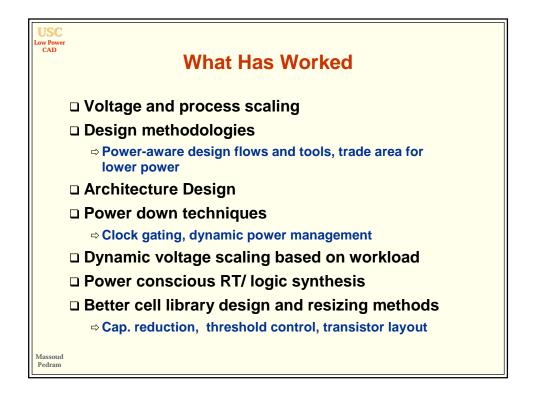

- □ Low power design is a critical area of research and development

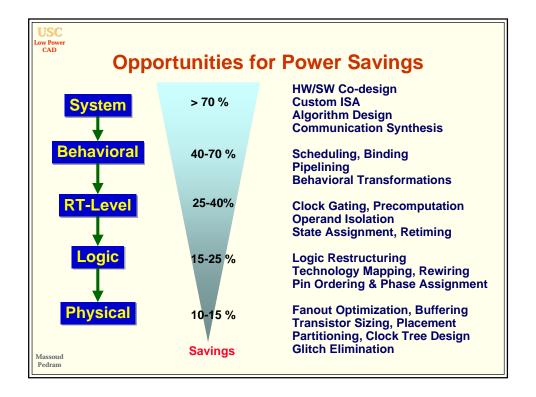

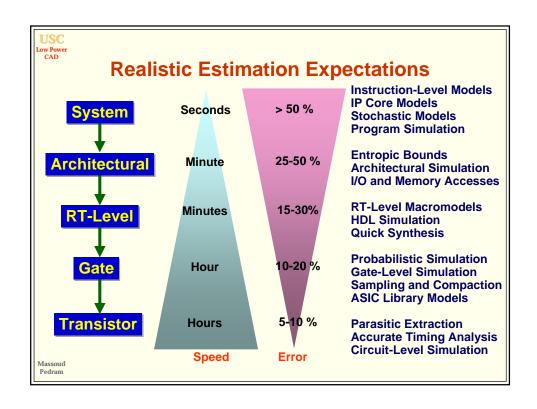

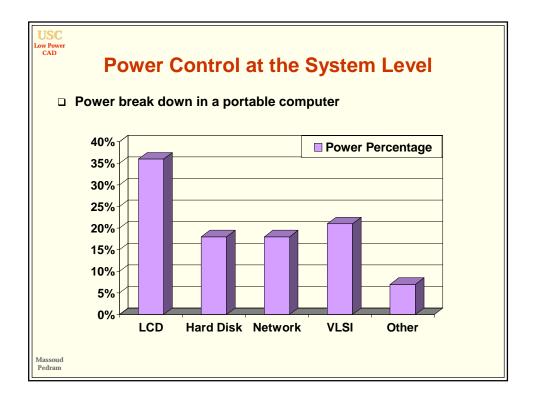

- Need early power analysis and estimation to enable high level optimizations

- □OS-directed power management and compiler-based power optimization hold the key to significant power reduction

Massoud Pedram